M5Stack Audio Module ES8388

-

Hello,

I am struggling with bring up audio module with es8388 codec on ESP-IDF. I trying to based on https://github.com/m5stack/M5Module-Audio/tree/main but this example is not true I2S bypass (it set bypass on chip in registers ES8388_DACCONTROL17 and ES8388_DACCONTROL20). But I need working solution with bypass audio ADC -> I2S -> DSP (bypass) -> I2S -> DAC. Anyone can help me with this codec?

Its my main file:#include "freertos/FreeRTOS.h" #include "es8388.h" #include "esp_log.h" #include "driver/i2c_master.h" #define I2C_PORT I2C_NUM_0 #define I2C_SDA 12 #define I2C_SCL 11 #define I2C_CLK_SPEED 100000 static const char *TAG = "ES8388"; static i2c_master_bus_handle_t bus_handle; static i2c_master_dev_handle_t dev_handle; static void i2c_init(void) { i2c_master_bus_config_t bus_cfg = { .i2c_port = I2C_PORT, .sda_io_num = I2C_SDA, .scl_io_num = I2C_SCL, .clk_source = I2C_CLK_SRC_DEFAULT, .flags.enable_internal_pullup = true, }; ESP_ERROR_CHECK(i2c_new_master_bus(&bus_cfg, &bus_handle)); i2c_device_config_t dev_cfg = { .device_address = ES8388_ADDR, .dev_addr_length = I2C_ADDR_BIT_LEN_7, .scl_speed_hz = I2C_CLK_SPEED, }; ESP_ERROR_CHECK(i2c_master_bus_add_device(bus_handle, &dev_cfg, &dev_handle)); ESP_LOGI(TAG, "ES8388 I2C device initialized (new API)"); } esp_err_t es_write_reg(uint8_t reg, uint8_t data) { uint8_t buf[2] = {reg, data}; return i2c_master_transmit(dev_handle, buf, sizeof(buf), -1); } esp_err_t es_read_reg(uint8_t reg, uint8_t *data) { esp_err_t res = i2c_master_transmit(dev_handle, ®, 1, -1); if (res != ESP_OK) return res; return i2c_master_receive(dev_handle, data, 1, -1); } esp_err_t es8388_init(void) { i2c_init(); esp_err_t res = ESP_OK; /* INITIALIZATION (BASED ON ES8388 USER GUIDE EXAMPLE) */ // Set Chip to Slave res |= es_write_reg(ES8388_MASTERMODE, 0x00); // Power down DEM and STM res |= es_write_reg(ES8388_CHIPPOWER, 0xFF); // Set same LRCK Set same LRCK res |= es_write_reg(ES8388_DACCONTROL21, 0x80); // Set Chip to Play&Record Mode res |= es_write_reg(ES8388_CONTROL1, 0x05); // Power Up Analog and Ibias res |= es_write_reg(ES8388_CONTROL2, 0x40); /* ADC setting */ // Micbias for Record res |= es_write_reg(ES8388_ADCPOWER, 0x00); // Enable Lin1/Rin1 (0x00 0x00) for Lin2/Rin2 (0x50 0x80) res |= es_write_reg(ES8388_ADCCONTROL2, 0x00); res |= es_write_reg(ES8388_ADCCONTROL3, 0x00); // PGA gain (0x88 - 24db) (0x77 - 21db) res |= es_write_reg(ES8388_ADCCONTROL1, 0x88); // SFI setting (i2s mode/16 bit) res |= es_write_reg(ES8388_ADCCONTROL4, 0x2C); // ADC MCLK/LCRK ratio (256) res |= es_write_reg(ES8388_ADCCONTROL5, 0x02); // set ADC digital volume res |= es_write_reg(ES8388_ADCCONTROL7, 0x28); res |= es_write_reg(ES8388_ADCCONTROL8, 0x00); res |= es_write_reg(ES8388_ADCCONTROL9, 0x00); // recommended ALC setting for VOICE refer to ES8388 MANUAL res |= es_write_reg(ES8388_ADCCONTROL10, 0x38); res |= es_write_reg(ES8388_ADCCONTROL11, 0xC0); res |= es_write_reg(ES8388_ADCCONTROL12, 0x12); res |= es_write_reg(ES8388_ADCCONTROL13, 0x06); res |= es_write_reg(ES8388_ADCCONTROL14, 0xC3); /* DAC setting */ // Power Up DAC& enable Lout/Rout res |= es_write_reg(ES8388_DACPOWER, 0x3F); // SFI setting (i2s mode/16 bit) res |= es_write_reg(ES8388_DACCONTROL1, 0x18); // DAC MCLK/LCRK ratio (256) res |= es_write_reg(ES8388_DACCONTROL2, 0x02); // unmute codec res |= es_write_reg(ES8388_DACCONTROL3, 0x00); // set DAC digital volume res |= es_write_reg(ES8388_DACCONTROL4, 0x05); res |= es_write_reg(ES8388_DACCONTROL5, 0x05); // Setup Mixer // (reg[16] 1B mic Amp, 0x09 direct;[reg 17-20] 0x90 DAC, 0x50 Mic Amp) res |= es_write_reg(ES8388_DACCONTROL16, 0x00); res |= es_write_reg(ES8388_DACCONTROL17, 0x90); // res |= es_write_reg(ES8388_DACCONTROL18, 0x38); //?? // res |= es_write_reg(ES8388_DACCONTROL19, 0x38); //?? res |= es_write_reg(ES8388_DACCONTROL20, 0x90); res |= es_write_reg(ES8388_DACCONTROL21, 0x80); // set Lout/Rout Volume -45db res |= es_write_reg(ES8388_DACCONTROL24, 0x12); res |= es_write_reg(ES8388_DACCONTROL25, 0x12); res |= es_write_reg(ES8388_DACCONTROL26, 0x00); res |= es_write_reg(ES8388_DACCONTROL27, 0x00); /* Power up DEM and STM */ res |= es_write_reg(ES8388_CHIPPOWER, 0x00); if(res == ESP_OK) { ESP_LOGI(TAG, "ES8388 initializes OK"); } else { ESP_LOGI(TAG, "ES8388 initializes FAIL"); } return res; } esp_err_t setMicGain(es_mic_gain_t gain) { esp_err_t res = ESP_OK; uint8_t controlValue = (gain << 4) | gain; res |= es_write_reg(ES8388_ADCCONTROL1, controlValue); return res; } uint8_t getMicGain() { static uint8_t data; es_read_reg(ES8388_ADCCONTROL1, &data); data = data & 0x0f; return data; } esp_err_t setADCInput(es_adc_input_t input) { esp_err_t res = ESP_OK; uint8_t reg = 0; res = es_read_reg(ES8388_ADCCONTROL2, ®); reg = reg & 0x0f; res |= es_write_reg(ES8388_ADCCONTROL2, reg | input); if (input == ADC_INPUT_LINPUT2_RINPUT2) { res |= es_write_reg(ES8388_ADCCONTROL3, 0x80); } return res; } esp_err_t setADCVolume(uint8_t volume) { esp_err_t res = ESP_OK; if (volume > 100) volume = 100; uint16_t steps = (uint16_t)(((100 - volume) * 192) / 100); uint8_t data = (uint8_t)(steps); res |= es_write_reg(ES8388_ADCCONTROL8, data); res |= es_write_reg(ES8388_ADCCONTROL9, data); return res; } esp_err_t setDACVolume(uint8_t volume) { esp_err_t res = ESP_OK; volume = (volume > 100) ? 100 : volume; uint8_t steps = (uint8_t)(((uint16_t)(volume) * 33 + 50) / 100); steps = (steps > 0x21) ? 0x21 : steps; res |= es_write_reg(ES8388_DACCONTROL24, steps); res |= es_write_reg(ES8388_DACCONTROL25, steps); return res; } esp_err_t setDACOutput(es_dac_output_t output) { esp_err_t res = ESP_OK; res |= es_write_reg(ES8388_DACPOWER, output); return res; } // mute Output esp_err_t setDACmute(bool mute) { uint8_t _reg; es_read_reg(ES8388_ADCCONTROL1, &_reg); esp_err_t res = ESP_OK; if (mute) res |= es_write_reg(ES8388_DACCONTROL3, _reg | 0x02); else res |= es_write_reg(ES8388_DACCONTROL3, _reg & ~(0x02)); return res; } esp_err_t setMixSourceSelect(es_mixsel_t lmixsel, es_mixsel_t rmixsel) { esp_err_t res = ESP_OK; uint8_t left_bits = 0, right_bits = 0; switch (lmixsel) { case MIXLIN1: left_bits = 0b000; break; case MIXLIN2: left_bits = 0b001; break; case MIXADC: left_bits = 0b011; break; case MIXRES: return false; default: return false; } switch (rmixsel) { case MIXLIN1: right_bits = 0b000; break; case MIXLIN2: right_bits = 0b001; break; case MIXADC: right_bits = 0b011; break; case MIXRES: return false; default: return false; } uint8_t data = (left_bits << 3) | (right_bits << 0); res |= es_write_reg(ES8388_DACCONTROL16, data); return res; } esp_err_t setBitsSample(es_module_t mode, es_bits_length_t bits_len) { esp_err_t res = ESP_OK; uint8_t reg = 0; int bits = (int)bits_len; if (mode == ES_MODULE_ADC || mode == ES_MODULE_ADC_DAC) { res = es_read_reg(ES8388_ADCCONTROL4, ®); reg = reg & 0xe3; res |= es_write_reg(ES8388_ADCCONTROL4, reg | (bits << 2)); } if (mode == ES_MODULE_DAC || mode == ES_MODULE_ADC_DAC) { res = es_read_reg(ES8388_DACCONTROL1, ®); reg = reg & 0xc7; res |= es_write_reg(ES8388_DACCONTROL1, reg | (bits << 3)); } return res; } esp_err_t setSampleRate(es_sample_rate_t rate) { esp_err_t res = ESP_OK; uint8_t masterMode = 0x00; uint8_t adcFsRatio = 0x02; uint8_t dacFsRatio = 0x02; uint8_t mclkDiv = 0x00; switch (rate) { case SAMPLE_RATE_8K: // MCLK=12.288MHz adcFsRatio = 0x0A; // 01010 (MCLK/1536) dacFsRatio = 0x0A; break; case SAMPLE_RATE_11K: // MCLK=11.2896MHz adcFsRatio = 0x07; // 00111 (MCLK/1024) dacFsRatio = 0x07; break; case SAMPLE_RATE_16K: // MCLK=12.288MHz adcFsRatio = 0x06; // 00110 (MCLK/768) dacFsRatio = 0x06; break; case SAMPLE_RATE_24K: // MCLK=12.288MHz adcFsRatio = 0x04; // 00100 (MCLK/512) dacFsRatio = 0x04; break; case SAMPLE_RATE_32K: // MCLK=12.288MHz adcFsRatio = 0x03; // 00011 (MCLK/384) dacFsRatio = 0x03; break; case SAMPLE_RATE_44K: // MCLK=11.2896MHz adcFsRatio = 0x02; // 00010 (MCLK/256) dacFsRatio = 0x02; mclkDiv = 0x40; break; case SAMPLE_RATE_48K: adcFsRatio = 0x02; // 00010 (MCLK/256) dacFsRatio = 0x02; break; default: return false; } res |= es_write_reg(ES8388_MASTERMODE, masterMode | mclkDiv); res |= es_write_reg(ES8388_ADCCONTROL5, adcFsRatio & 0x1F); res |= es_write_reg(ES8388_DACCONTROL2, dacFsRatio & 0x1F); return res; }This is my driver

es8388.c:#include "freertos/FreeRTOS.h" #include "es8388.h" #include "esp_log.h" #include "driver/i2c_master.h" #define I2C_PORT I2C_NUM_0 #define I2C_SDA 12 #define I2C_SCL 11 #define I2C_CLK_SPEED 100000 static const char *TAG = "ES8388"; static i2c_master_bus_handle_t bus_handle; static i2c_master_dev_handle_t dev_handle; static void i2c_init(void) { i2c_master_bus_config_t bus_cfg = { .i2c_port = I2C_PORT, .sda_io_num = I2C_SDA, .scl_io_num = I2C_SCL, .clk_source = I2C_CLK_SRC_DEFAULT, .flags.enable_internal_pullup = true, }; ESP_ERROR_CHECK(i2c_new_master_bus(&bus_cfg, &bus_handle)); i2c_device_config_t dev_cfg = { .device_address = ES8388_ADDR, .dev_addr_length = I2C_ADDR_BIT_LEN_7, .scl_speed_hz = I2C_CLK_SPEED, }; ESP_ERROR_CHECK(i2c_master_bus_add_device(bus_handle, &dev_cfg, &dev_handle)); ESP_LOGI(TAG, "ES8388 I2C device initialized (new API)"); } esp_err_t es_write_reg(uint8_t reg, uint8_t data) { uint8_t buf[2] = {reg, data}; return i2c_master_transmit(dev_handle, buf, sizeof(buf), -1); } esp_err_t es_read_reg(uint8_t reg, uint8_t *data) { esp_err_t res = i2c_master_transmit(dev_handle, ®, 1, -1); if (res != ESP_OK) return res; return i2c_master_receive(dev_handle, data, 1, -1); } esp_err_t es8388_init(void) { i2c_init(); esp_err_t res = ESP_OK; /* INITIALIZATION (BASED ON ES8388 USER GUIDE EXAMPLE) */ // Set Chip to Slave res |= es_write_reg(ES8388_MASTERMODE, 0x00); // Power down DEM and STM res |= es_write_reg(ES8388_CHIPPOWER, 0xFF); // Set same LRCK Set same LRCK res |= es_write_reg(ES8388_DACCONTROL21, 0x80); // Set Chip to Play&Record Mode res |= es_write_reg(ES8388_CONTROL1, 0x05); // Power Up Analog and Ibias res |= es_write_reg(ES8388_CONTROL2, 0x40); /* ADC setting */ // Micbias for Record res |= es_write_reg(ES8388_ADCPOWER, 0x00); // Enable Lin1/Rin1 (0x00 0x00) for Lin2/Rin2 (0x50 0x80) res |= es_write_reg(ES8388_ADCCONTROL2, 0x00); res |= es_write_reg(ES8388_ADCCONTROL3, 0x00); // PGA gain (0x88 - 24db) (0x77 - 21db) res |= es_write_reg(ES8388_ADCCONTROL1, 0x88); // SFI setting (i2s mode/16 bit) res |= es_write_reg(ES8388_ADCCONTROL4, 0x2C); // ADC MCLK/LCRK ratio (256) res |= es_write_reg(ES8388_ADCCONTROL5, 0x02); // set ADC digital volume res |= es_write_reg(ES8388_ADCCONTROL7, 0x28); res |= es_write_reg(ES8388_ADCCONTROL8, 0x00); res |= es_write_reg(ES8388_ADCCONTROL9, 0x00); // recommended ALC setting for VOICE refer to ES8388 MANUAL res |= es_write_reg(ES8388_ADCCONTROL10, 0x38); res |= es_write_reg(ES8388_ADCCONTROL11, 0xC0); res |= es_write_reg(ES8388_ADCCONTROL12, 0x12); res |= es_write_reg(ES8388_ADCCONTROL13, 0x06); res |= es_write_reg(ES8388_ADCCONTROL14, 0xC3); /* DAC setting */ // Power Up DAC& enable Lout/Rout res |= es_write_reg(ES8388_DACPOWER, 0x3F); // SFI setting (i2s mode/16 bit) res |= es_write_reg(ES8388_DACCONTROL1, 0x18); // DAC MCLK/LCRK ratio (256) res |= es_write_reg(ES8388_DACCONTROL2, 0x02); // unmute codec res |= es_write_reg(ES8388_DACCONTROL3, 0x00); // set DAC digital volume res |= es_write_reg(ES8388_DACCONTROL4, 0x05); res |= es_write_reg(ES8388_DACCONTROL5, 0x05); // Setup Mixer // (reg[16] 1B mic Amp, 0x09 direct;[reg 17-20] 0x90 DAC, 0x50 Mic Amp) res |= es_write_reg(ES8388_DACCONTROL16, 0x00); res |= es_write_reg(ES8388_DACCONTROL17, 0xD0); // res |= es_write_reg(ES8388_DACCONTROL18, 0x38); //?? // res |= es_write_reg(ES8388_DACCONTROL19, 0x38); //?? res |= es_write_reg(ES8388_DACCONTROL20, 0xD0); res |= es_write_reg(ES8388_DACCONTROL21, 0x80); // set Lout/Rout Volume -45db res |= es_write_reg(ES8388_DACCONTROL24, 0x12); res |= es_write_reg(ES8388_DACCONTROL25, 0x12); res |= es_write_reg(ES8388_DACCONTROL26, 0x00); res |= es_write_reg(ES8388_DACCONTROL27, 0x00); /* Power up DEM and STM */ res |= es_write_reg(ES8388_CHIPPOWER, 0x00); if(res == ESP_OK) { ESP_LOGI(TAG, "ES8388 initializes OK"); } else { ESP_LOGI(TAG, "ES8388 initializes FAIL"); } return res; } esp_err_t setMicGain(es_mic_gain_t gain) { esp_err_t res = ESP_OK; uint8_t controlValue = (gain << 4) | gain; res |= es_write_reg(ES8388_ADCCONTROL1, controlValue); return res; } uint8_t getMicGain() { static uint8_t data; es_read_reg(ES8388_ADCCONTROL1, &data); data = data & 0x0f; return data; } esp_err_t setADCInput(es_adc_input_t input) { esp_err_t res = ESP_OK; uint8_t reg = 0; res = es_read_reg(ES8388_ADCCONTROL2, ®); reg = reg & 0x0f; res |= es_write_reg(ES8388_ADCCONTROL2, reg | input); if (input == ADC_INPUT_LINPUT2_RINPUT2) { res |= es_write_reg(ES8388_ADCCONTROL3, 0x80); } return res; } esp_err_t setADCVolume(uint8_t volume) { esp_err_t res = ESP_OK; if (volume > 100) volume = 100; uint16_t steps = (uint16_t)(((100 - volume) * 192) / 100); uint8_t data = (uint8_t)(steps); res |= es_write_reg(ES8388_ADCCONTROL8, data); res |= es_write_reg(ES8388_ADCCONTROL9, data); return res; } esp_err_t setDACVolume(uint8_t volume) { esp_err_t res = ESP_OK; volume = (volume > 100) ? 100 : volume; uint8_t steps = (uint8_t)(((uint16_t)(volume) * 33 + 50) / 100); steps = (steps > 0x21) ? 0x21 : steps; res |= es_write_reg(ES8388_DACCONTROL24, steps); res |= es_write_reg(ES8388_DACCONTROL25, steps); return res; } esp_err_t setDACOutput(es_dac_output_t output) { esp_err_t res = ESP_OK; res |= es_write_reg(ES8388_DACPOWER, output); return res; } // mute Output esp_err_t setDACmute(bool mute) { uint8_t _reg; es_read_reg(ES8388_ADCCONTROL1, &_reg); esp_err_t res = ESP_OK; if (mute) res |= es_write_reg(ES8388_DACCONTROL3, _reg | 0x02); else res |= es_write_reg(ES8388_DACCONTROL3, _reg & ~(0x02)); return res; } esp_err_t setMixSourceSelect(es_mixsel_t lmixsel, es_mixsel_t rmixsel) { esp_err_t res = ESP_OK; uint8_t left_bits = 0, right_bits = 0; switch (lmixsel) { case MIXLIN1: left_bits = 0b000; break; case MIXLIN2: left_bits = 0b001; break; case MIXADC: left_bits = 0b011; break; case MIXRES: return false; default: return false; } switch (rmixsel) { case MIXLIN1: right_bits = 0b000; break; case MIXLIN2: right_bits = 0b001; break; case MIXADC: right_bits = 0b011; break; case MIXRES: return false; default: return false; } uint8_t data = (left_bits << 3) | (right_bits << 0); res |= es_write_reg(ES8388_DACCONTROL16, data); return res; } esp_err_t setBitsSample(es_module_t mode, es_bits_length_t bits_len) { esp_err_t res = ESP_OK; uint8_t reg = 0; int bits = (int)bits_len; if (mode == ES_MODULE_ADC || mode == ES_MODULE_ADC_DAC) { res = es_read_reg(ES8388_ADCCONTROL4, ®); reg = reg & 0xe3; res |= es_write_reg(ES8388_ADCCONTROL4, reg | (bits << 2)); } if (mode == ES_MODULE_DAC || mode == ES_MODULE_ADC_DAC) { res = es_read_reg(ES8388_DACCONTROL1, ®); reg = reg & 0xc7; res |= es_write_reg(ES8388_DACCONTROL1, reg | (bits << 3)); } return res; } esp_err_t setSampleRate(es_sample_rate_t rate) { esp_err_t res = ESP_OK; uint8_t masterMode = 0x00; uint8_t adcFsRatio = 0x02; uint8_t dacFsRatio = 0x02; uint8_t mclkDiv = 0x00; switch (rate) { case SAMPLE_RATE_8K: // MCLK=12.288MHz adcFsRatio = 0x0A; // 01010 (MCLK/1536) dacFsRatio = 0x0A; break; case SAMPLE_RATE_11K: // MCLK=11.2896MHz adcFsRatio = 0x07; // 00111 (MCLK/1024) dacFsRatio = 0x07; break; case SAMPLE_RATE_16K: // MCLK=12.288MHz adcFsRatio = 0x06; // 00110 (MCLK/768) dacFsRatio = 0x06; break; case SAMPLE_RATE_24K: // MCLK=12.288MHz adcFsRatio = 0x04; // 00100 (MCLK/512) dacFsRatio = 0x04; break; case SAMPLE_RATE_32K: // MCLK=12.288MHz adcFsRatio = 0x03; // 00011 (MCLK/384) dacFsRatio = 0x03; break; case SAMPLE_RATE_44K: // MCLK=11.2896MHz adcFsRatio = 0x02; // 00010 (MCLK/256) dacFsRatio = 0x02; mclkDiv = 0x40; break; case SAMPLE_RATE_48K: adcFsRatio = 0x02; // 00010 (MCLK/256) dacFsRatio = 0x02; break; default: return false; } res |= es_write_reg(ES8388_MASTERMODE, masterMode | mclkDiv); res |= es_write_reg(ES8388_ADCCONTROL5, adcFsRatio & 0x1F); res |= es_write_reg(ES8388_DACCONTROL2, dacFsRatio & 0x1F); return res; }es8388.h:

/* * es8388.h * * Created on: Jul 31, 2021 * Author: xenir */ #ifndef ES8388_H_ #define ES8388_H_ #include "stdbool.h" #include "stdint.h" /** * @file ES8388_registers.h * @brief Definitions for ES8388 audio codec registers */ /** * @brief I2C device address for ES8388 */ #define ES8388_ADDR (0x10) /* ES8388 control registers */ /** * @brief Control register 1 - System control and clock settings */ #define ES8388_CONTROL1 (0x00) /** * @brief Control register 2 - Interface format and clock mode */ #define ES8388_CONTROL2 (0x01) /** * @brief Chip power management register */ #define ES8388_CHIPPOWER (0x02) /** * @brief ADC power control register */ #define ES8388_ADCPOWER (0x03) /** * @brief DAC power control register */ #define ES8388_DACPOWER (0x04) /** * @brief Low power control register 1 */ #define ES8388_CHIPLOPOW1 (0x05) /** * @brief Low power control register 2 */ #define ES8388_CHIPLOPOW2 (0x06) /** * @brief Analog volume management control */ #define ES8388_ANAVOLMANAG (0x07) /** * @brief Master/slave mode control */ #define ES8388_MASTERMODE (0x08) /* ADC registers */ /** * @brief ADC control 1 - Input selection and PGA gain */ #define ES8388_ADCCONTROL1 (0x09) /** @brief ADC control 2 - Digital mic settings */ #define ES8388_ADCCONTROL2 (0x0a) /** * @brief ADC control 3 - High-pass filter and ADC mode */ #define ES8388_ADCCONTROL3 (0x0b) /** * @brief ADC control 4 - Sample rate and clock divider */ #define ES8388_ADCCONTROL4 (0x0c) /** * @brief ADC control 5 - Digital volume control */ #define ES8388_ADCCONTROL5 (0x0d) /** * @brief ADC control 6 - ALC settings 1 */ #define ES8388_ADCCONTROL6 (0x0e) /** * @brief ADC control 7 - ALC settings 2 */ #define ES8388_ADCCONTROL7 (0x0f) /** * @brief ADC control 8 - ALC settings 3 */ #define ES8388_ADCCONTROL8 (0x10) /** * @brief ADC control 9 - Noise gate control */ #define ES8388_ADCCONTROL9 (0x11) /** * @brief ADC control 10 - Zero detection */ #define ES8388_ADCCONTROL10 (0x12) /** * @brief ADC control 11 - ALC enable and mode */ #define ES8388_ADCCONTROL11 (0x13) /** * @brief ADC control 12 - Left channel volume */ #define ES8388_ADCCONTROL12 (0x14) /** * @brief ADC control 13 - Right channel volume */ #define ES8388_ADCCONTROL13 (0x15) /** * @brief ADC control 14 - Analog PGA control */ #define ES8388_ADCCONTROL14 (0x16) /* DAC registers */ /** * @brief DAC control 1 - Soft ramp and volume control */ #define ES8388_DACCONTROL1 (0x17) /** * @brief DAC control 2 - DAC interface format */ #define ES8388_DACCONTROL2 (0x18) /** * @brief DAC control 3 - De-emphasis and mute control */ #define ES8388_DACCONTROL3 (0x19) /** * @brief DAC control 4 - Sample rate and clock divider */ #define ES8388_DACCONTROL4 (0x1a) /** * @brief DAC control 5 - Digital volume left */ #define ES8388_DACCONTROL5 (0x1b) /** * @brief DAC control 6 - Digital volume right */ #define ES8388_DACCONTROL6 (0x1c) /** * @brief DAC control 7 - Volume mixer control */ #define ES8388_DACCONTROL7 (0x1d) /** * @brief DAC control 8 - Mixer settings */ #define ES8388_DACCONTROL8 (0x1e) /** * @brief DAC control 9 - Channel swap and mute */ #define ES8388_DACCONTROL9 (0x1f) /** * @brief DAC control 10 - Zero cross detection */ #define ES8388_DACCONTROL10 (0x20) /** * @brief DAC control 11 - Volume ramp rate */ #define ES8388_DACCONTROL11 (0x21) /** * @brief DAC control 12 - Power management */ #define ES8388_DACCONTROL12 (0x22) /** * @brief DAC control 13 - Analog output control */ #define ES8388_DACCONTROL13 (0x23) /** * @brief DAC control 14 - Output phase control */ #define ES8388_DACCONTROL14 (0x24) /** * @brief DAC control 15 - Output level control */ #define ES8388_DACCONTROL15 (0x25) /** * @brief DAC control 16 - Mixer volume left */ #define ES8388_DACCONTROL16 (0x26) /** * @brief DAC control 17 - Mixer volume right */ #define ES8388_DACCONTROL17 (0x27) /** * @brief DAC control 18 - ALC control 1 */ #define ES8388_DACCONTROL18 (0x28) /** * @brief DAC control 19 - ALC control 2 */ #define ES8388_DACCONTROL19 (0x29) /** * @brief DAC control 20 - ALC control 3 */ #define ES8388_DACCONTROL20 (0x2a) /** * @brief DAC control 21 - ALC control 4 */ #define ES8388_DACCONTROL21 (0x2b) /** * @brief DAC control 22 - Noise gate control */ #define ES8388_DACCONTROL22 (0x2c) /** * @brief DAC control 23 - Zero detection */ #define ES8388_DACCONTROL23 (0x2d) /** * @brief DAC control 24 - Output mute control * */ #define ES8388_DACCONTROL24 (0x2e) /** * @brief DAC control 25 - Volume bypass control */ #define ES8388_DACCONTROL25 (0x2f) /** * @brief DAC control 26 - Output phase control */ #define ES8388_DACCONTROL26 (0x30) /** * @brief DAC control 27 - Volume fade control */ #define ES8388_DACCONTROL27 (0x31) /** * @brief DAC control 28 - Power on delay control */ #define ES8388_DACCONTROL28 (0x32) /** * @brief DAC control 29 - Output driver control */ #define ES8388_DACCONTROL29 (0x33) /** * @brief DAC control 30 - Reserved/test mode */ #define ES8388_DACCONTROL30 (0x34) /** * @brief Mixer input source selection * @note Mixer configuration affects audio path routing */ typedef enum { MIXLIN1, /**< Direct line input 1 (unprocessed signal path) */ MIXLIN2, /**< Direct line input 2 (alternative signal path) */ MIXRES, /**< Reserved mixer source (do not use in normal operation) */ MIXADC /**< Processed signal from ADC/ALC (with automatic level control) */ } es_mixsel_t; /** * @brief ES8388 functional module selection */ typedef enum { ES_MODULE_MIN = -1, /**< Minimum module selector (validation flag) */ ES_MODULE_ADC = 0x01, /**< Enable ADC module */ ES_MODULE_DAC = 0x02, /**< Enable DAC module */ ES_MODULE_ADC_DAC = 0x03, /**< Enable both ADC and DAC modules */ ES_MODULE_LINE = 0x04, /**< Line-in/out interface control */ ES_MODULE_MAX /**< Maximum module selector (validation flag) */ } es_module_t; /** * @brief Audio data bit length configuration * @note Actual supported resolution depends on hardware capabilities */ typedef enum { BIT_LENGTH_MIN = -1, /**< Minimum bit length flag (validation) */ BIT_LENGTH_16BITS = 0x03, /**< 16-bit word length */ BIT_LENGTH_18BITS = 0x02, /**< 18-bit word length */ BIT_LENGTH_20BITS = 0x01, /**< 20-bit word length */ BIT_LENGTH_24BITS = 0x00, /**< 24-bit word length (typical default) */ BIT_LENGTH_32BITS = 0x04, /**< 32-bit word length */ BIT_LENGTH_MAX, /**< Maximum bit length flag (validation) */ } es_bits_length_t; /** * @brief ADC input channel selection * @note Configuration affects both left and right channels */ typedef enum { ADC_INPUT_LINPUT1_RINPUT1 = 0x00, /**< Use input 1 for both channels */ ADC_INPUT_LINPUT2_RINPUT2 = 0x10, /**< Use input 2 for both channels */ ADC_INPUT_DIFFERENCE1 = 0xf0, /**< Differential input configuration */ } es_adc_input_t; /** * @brief DAC output channel selection * @note Multiple outputs can be combined using bitwise OR */ typedef enum { DAC_OUTPUT_OUT1 = 0x30, /**< Enable output channel 1 */ DAC_OUTPUT_OUT2 = 0x0C, /**< Enable output channel 2 */ DAC_OUTPUT_ALL = 0x3c, /**< Enable all output channels */ } es_dac_output_t; /** * @brief Microphone gain settings * @note Values represent gain steps in 3dB increments */ typedef enum { MIC_GAIN_0DB = 0, /**< 0dB microphone gain */ MIC_GAIN_3DB, /**< 3dB microphone gain */ MIC_GAIN_6DB, /**< 6dB microphone gain */ MIC_GAIN_9DB, /**< 9dB microphone gain */ MIC_GAIN_12DB, /**< 12dB microphone gain */ MIC_GAIN_15DB, /**< 15dB microphone gain */ MIC_GAIN_18DB, /**< 18dB microphone gain */ MIC_GAIN_21DB, /**< 21dB microphone gain */ MIC_GAIN_24DB, /**< 24dB microphone gain (maximum) */ } es_mic_gain_t; typedef enum { SAMPLE_RATE_8K = 0, /**< 8000 Hz sampling rate */ SAMPLE_RATE_11K, /**< 11025 Hz sampling rate */ SAMPLE_RATE_16K, /**< 16000 Hz sampling rate */ SAMPLE_RATE_24K, /**< 24000 Hz sampling rate */ SAMPLE_RATE_32K, /**< 32000 Hz sampling rate */ SAMPLE_RATE_44K, /**< 44100 Hz sampling rate (CD quality) */ SAMPLE_RATE_48K /**< 48000 Hz sampling rate (professional audio) */ } es_sample_rate_t; // API esp_err_t es_write_reg(uint8_t reg, uint8_t data); esp_err_t es_read_reg(uint8_t reg, uint8_t *data); esp_err_t es8388_init(void); esp_err_t setMicGain(es_mic_gain_t gain); uint8_t getMicGain(); esp_err_t setADCInput(es_adc_input_t input); esp_err_t setADCVolume(uint8_t volume); esp_err_t setDACVolume(uint8_t volume); esp_err_t setDACOutput(es_dac_output_t output); esp_err_t setDACmute(bool mute); esp_err_t setMixSourceSelect(es_mixsel_t lmixsel, es_mixsel_t rmixsel); esp_err_t setBitsSample(es_module_t mode, es_bits_length_t bits_len); esp_err_t setSampleRate(es_sample_rate_t rate); void es8388_dump_registers(void); esp_err_t es8388_check_connection(void); #endif /* ES8388_H_ */Maybe is something wrong with my I2S config?

-

I already run it with this codes:

my main file audioFX.c:

#include "freertos/FreeRTOS.h" #include "freertos/task.h" #include "esp_log.h" #include "es8388.h" #include "driver/i2s_std.h" static char *TAG = "app_main"; // I2S config #define I2S_NUM (0) #define SAMPLE_RATE (48000) #define I2S_MCLK 0 #define I2S_SCLK 7 #define I2S_WS 6 #define I2S_DOUT 13 #define I2S_DIN 14 #define DMA_DESC_NUM 8 #define DMA_FRAME_NUM 256 #define AUDIO_BUF_SAMPLES 256 #define FRAMES_PER_BLOCK 256 #define CHANNELS 2 static i2s_chan_handle_t tx_handle; static i2s_chan_handle_t rx_handle; static void codec_init(void) { es8388_init(); setADCInput(ADC_INPUT_LINPUT1_RINPUT1); setADCVolume(100); setDACVolume(60); setDACOutput(DAC_OUTPUT_OUT1); setBitsSample(ES_MODULE_LINE, BIT_LENGTH_16BITS); setSampleRate(SAMPLE_RATE_48K); } static void init_i2s(void) { /* ---------- CHANNEL CONFIG ---------- */ i2s_chan_config_t chan_cfg = { .id = I2S_NUM, .role = I2S_ROLE_MASTER, .dma_desc_num = DMA_DESC_NUM, .dma_frame_num = DMA_FRAME_NUM, .auto_clear = true, .intr_priority = 0, }; ESP_ERROR_CHECK(i2s_new_channel(&chan_cfg, &tx_handle, &rx_handle)); /* ---------- STANDARD I2S CONFIG ---------- */ i2s_std_config_t std_cfg = { .clk_cfg = { .sample_rate_hz = SAMPLE_RATE, .clk_src = I2S_CLK_SRC_DEFAULT, .ext_clk_freq_hz = 0, .mclk_multiple = I2S_MCLK_MULTIPLE_256, }, .slot_cfg = { .data_bit_width = I2S_DATA_BIT_WIDTH_16BIT, .slot_bit_width = I2S_SLOT_BIT_WIDTH_16BIT, .slot_mode = I2S_SLOT_MODE_STEREO, .slot_mask = I2S_STD_SLOT_BOTH, .ws_width = 16, .ws_pol = false, .bit_shift = true, .left_align = true, .big_endian = false, .bit_order_lsb = false, }, .gpio_cfg = { .mclk = I2S_MCLK, .bclk = I2S_SCLK, .ws = I2S_WS, .dout = I2S_DOUT, .din = I2S_DIN, .invert_flags = { .mclk_inv = false, .bclk_inv = false, .ws_inv = false, }, }, }; /* ---------- INIT + ENABLE ---------- */ ESP_ERROR_CHECK(i2s_channel_init_std_mode(tx_handle, &std_cfg)); ESP_ERROR_CHECK(i2s_channel_init_std_mode(rx_handle, &std_cfg)); ESP_ERROR_CHECK(i2s_channel_enable(tx_handle)); ESP_ERROR_CHECK(i2s_channel_enable(rx_handle)); } #define SINE_SAMPLES 48 static const int16_t sine_lut[SINE_SAMPLES] = { 0, 3916, 7764, 11480, 15000, 18263, 21213, 23800, 25981, 27716, 28978, 29750, 30000, 29750, 28978, 27716, 25981, 23800, 21213, 18263, 15000, 11480, 7764, 3916, 0, -3916, -7764,-11480,-15000,-18263,-21213,-23800, -25981,-27716,-28978,-29750,-30000,-29750,-28978,-27716, -25981,-23800,-21213,-18263,-15000,-11480, -7764, -3916 }; int16_t sine_1khz_next_sample(void) { static uint32_t idx = 0; int16_t sample = sine_lut[idx]; idx++; if (idx >= SINE_SAMPLES) { idx = 0; } return sample; } static void audioTask(void *arg) { ESP_LOGI("AUDIO", "audioTask STARTED"); // Bufor I2S (interleaved: L R L R ...) int16_t i2s_buf[FRAMES_PER_BLOCK * CHANNELS]; // channels int16_t left[FRAMES_PER_BLOCK]; int16_t right[FRAMES_PER_BLOCK]; size_t bytes_read = 0; size_t bytes_written = 0; while (true) { /* ===== RX ===== */ esp_err_t err = i2s_channel_read( rx_handle, i2s_buf, sizeof(i2s_buf), &bytes_read, portMAX_DELAY ); if (err != ESP_OK || bytes_read == 0) { continue; } size_t frames = bytes_read / (CHANNELS * sizeof(int16_t)); /* ===== DEINTERLEAVE ===== */ for (size_t i = 0; i < frames; i++) { left[i] = i2s_buf[2 * i]; // L right[i] = i2s_buf[2 * i + 1]; // R } /* ===== DSP ===== */ for (size_t i = 0; i < frames; i++) { left[i] = left[i] * 1.0f; right[i] = right[i] * 1.0f; // left[i] = sine_1khz_next_sample(); // right[i] = 0; } /* ===== INTERLEAVE ===== */ for (size_t i = 0; i < frames; i++) { i2s_buf[2 * i] = left[i]; // L i2s_buf[2 * i + 1] = right[i]; // R } /* ===== TX ===== */ i2s_channel_write( tx_handle, i2s_buf, frames * CHANNELS * sizeof(int16_t), &bytes_written, portMAX_DELAY ); } } void app_main(void) { codec_init(); init_i2s(); BaseType_t ret = xTaskCreate( audioTask, "audioTask", 4096, NULL, 5, NULL ); if (ret != pdPASS) { ESP_LOGE(TAG, "audioTask creation FAILED"); } else { ESP_LOGI(TAG, "audioTask created OK"); } }es8388.c:

#include "freertos/FreeRTOS.h" #include "es8388.h" #include "esp_log.h" #include "driver/i2c_master.h" #define I2C_PORT I2C_NUM_0 #define I2C_SDA 12 #define I2C_SCL 11 #define I2C_CLK_SPEED 100000 static const char *TAG = "ES8388"; static i2c_master_bus_handle_t bus_handle; static i2c_master_dev_handle_t dev_handle; static void i2c_init(void) { i2c_master_bus_config_t bus_cfg = { .i2c_port = I2C_PORT, .sda_io_num = I2C_SDA, .scl_io_num = I2C_SCL, .clk_source = I2C_CLK_SRC_DEFAULT, .flags.enable_internal_pullup = true, }; ESP_ERROR_CHECK(i2c_new_master_bus(&bus_cfg, &bus_handle)); i2c_device_config_t dev_cfg = { .device_address = ES8388_ADDR, .dev_addr_length = I2C_ADDR_BIT_LEN_7, .scl_speed_hz = I2C_CLK_SPEED, }; ESP_ERROR_CHECK(i2c_master_bus_add_device(bus_handle, &dev_cfg, &dev_handle)); ESP_LOGI(TAG, "ES8388 I2C device initialized (new API)"); } esp_err_t es_write_reg(uint8_t reg, uint8_t data) { uint8_t buf[2] = {reg, data}; return i2c_master_transmit(dev_handle, buf, sizeof(buf), -1); } esp_err_t es_read_reg(uint8_t reg, uint8_t *data) { esp_err_t res = i2c_master_transmit(dev_handle, ®, 1, -1); if (res != ESP_OK) return res; return i2c_master_receive(dev_handle, data, 1, -1); } esp_err_t es8388_init(void) { i2c_init(); esp_err_t res = ESP_OK; /* INITIALIZATION (BASED ON ES8388 USER GUIDE EXAMPLE) */ // Set Chip to Slave res |= es_write_reg(ES8388_MASTERMODE, 0x00); // Power down DEM and STM res |= es_write_reg(ES8388_CHIPPOWER, 0xFF); // Set same LRCK Set same LRCK res |= es_write_reg(ES8388_DACCONTROL21, 0x80); // Set Chip to Play&Record Mode res |= es_write_reg(ES8388_CONTROL1, 0x14); // Power Up Analog and Ibias res |= es_write_reg(ES8388_CONTROL2, 0x40); /* ADC setting */ // Micbias for Record res |= es_write_reg(ES8388_ADCPOWER, 0x00); // Enable Lin1/Rin1 (0x00 0x00) for Lin2/Rin2 (0x50 0x80) res |= es_write_reg(ES8388_ADCCONTROL2, 0x00); res |= es_write_reg(ES8388_ADCCONTROL3, 0x00); // PGA gain (0x88 - 24db) (0x77 - 21db) res |= es_write_reg(ES8388_ADCCONTROL1, 0x88); // SFI setting (i2s mode/16 bit) res |= es_write_reg(ES8388_ADCCONTROL4, 0x0C); // ADC MCLK/LCRK ratio (256) res |= es_write_reg(ES8388_ADCCONTROL5, 0x02); // disable HPF res |= es_write_reg(ES8388_ADCCONTROL6, 0x00); // set ADC digital volume res |= es_write_reg(ES8388_ADCCONTROL7, 0x00); res |= es_write_reg(ES8388_ADCCONTROL8, 0x00); res |= es_write_reg(ES8388_ADCCONTROL9, 0x00); // recommended ALC setting for VOICE refer to ES8388 MANUAL res |= es_write_reg(ES8388_ADCCONTROL10, 0x38); res |= es_write_reg(ES8388_ADCCONTROL11, 0xC0); res |= es_write_reg(ES8388_ADCCONTROL12, 0x12); res |= es_write_reg(ES8388_ADCCONTROL13, 0x06); res |= es_write_reg(ES8388_ADCCONTROL14, 0xC2); /* DAC setting */ // Power Up DAC& enable Lout/Rout res |= es_write_reg(ES8388_DACPOWER, 0x3F); // SFI setting (i2s mode/16 bit) res |= es_write_reg(ES8388_DACCONTROL1, 0x18); // DAC MCLK/LCRK ratio (256) res |= es_write_reg(ES8388_DACCONTROL2, 0x02); // unmute codec res |= es_write_reg(ES8388_DACCONTROL3, 0x00); // set DAC digital volume res |= es_write_reg(ES8388_DACCONTROL4, 0x05); res |= es_write_reg(ES8388_DACCONTROL5, 0x05); // Setup Mixer // (reg[16] 1B mic Amp, 0x09 direct;[reg 17-20] 0x90 DAC, 0x50 Mic Amp) res |= es_write_reg(ES8388_DACCONTROL16, 0x00); res |= es_write_reg(ES8388_DACCONTROL17, 0x90); // res |= es_write_reg(ES8388_DACCONTROL18, 0x38); //?? // res |= es_write_reg(ES8388_DACCONTROL19, 0x38); //?? res |= es_write_reg(ES8388_DACCONTROL20, 0x90); res |= es_write_reg(ES8388_DACCONTROL21, 0x80); // set Lout/Rout Volume -45db res |= es_write_reg(ES8388_DACCONTROL24, 0x12); res |= es_write_reg(ES8388_DACCONTROL25, 0x12); res |= es_write_reg(ES8388_DACCONTROL26, 0x00); res |= es_write_reg(ES8388_DACCONTROL27, 0x00); /* Power up DEM and STM */ res |= es_write_reg(ES8388_CHIPPOWER, 0x00); if(res == ESP_OK) { ESP_LOGI(TAG, "ES8388 initializes OK"); } else { ESP_LOGI(TAG, "ES8388 initializes FAIL"); } return res; } esp_err_t es8388_init2(void) { i2c_init(); esp_err_t res = ESP_OK; /* mute DAC during setup, power up all systems, slave mode */ res |= es_write_reg(ES8388_DACCONTROL3, 0x04); res |= es_write_reg(ES8388_CONTROL2, 0x50); res |= es_write_reg(ES8388_CHIPPOWER, 0x00); res |= es_write_reg(ES8388_MASTERMODE, 0x00); /* power up DAC and enable LOUT1+2 / ROUT1+2, ADC sample rate = DAC sample rate */ res |= es_write_reg(ES8388_DACPOWER, 0x3e); res |= es_write_reg(ES8388_CONTROL1, 0x12); /* DAC I2S setup: 16 bit word length, I2S format; MCLK / Fs = 256*/ res |= es_write_reg(ES8388_DACCONTROL1, 0x18); res |= es_write_reg(ES8388_DACCONTROL2, 0x02); /* DAC to output route mixer configuration: ADC MIX TO OUTPUT */ res |= es_write_reg(ES8388_DACCONTROL16, 0x1B); res |= es_write_reg(ES8388_DACCONTROL17, 0x90); res |= es_write_reg(ES8388_DACCONTROL20, 0x90); /* DAC and ADC use same LRCK, enable MCLK input; output resistance setup */ res |= es_write_reg(ES8388_DACCONTROL21, 0x80); res |= es_write_reg(ES8388_DACCONTROL23, 0x00); /* DAC volume control: 0dB (maximum, unattented) */ res |= es_write_reg(ES8388_DACCONTROL5, 0x00); res |= es_write_reg(ES8388_DACCONTROL4, 0x00); /* power down ADC while configuring; volume: +9dB for both channels */ res |= es_write_reg(ES8388_ADCPOWER, 0xff); res |= es_write_reg(ES8388_ADCCONTROL1, 0x88); /* select LINPUT1 / RINPUT1 as ADC input; stereo; 16 bit word length, format right-justified, MCLK / Fs = 256 */ res |= es_write_reg(ES8388_ADCCONTROL2, 0x00); res |= es_write_reg(ES8388_ADCCONTROL3, 0x00); res |= es_write_reg(ES8388_ADCCONTROL4, 0x0C); res |= es_write_reg(ES8388_ADCCONTROL5, 0x02); /* set ADC volume */ res |= es_write_reg(ES8388_ADCCONTROL8, 0x20); res |= es_write_reg(ES8388_ADCCONTROL9, 0x20); /* set LOUT1 / ROUT1 volume: 0dB (unattenuated) */ res |= es_write_reg(ES8388_DACCONTROL24, 0x1e); res |= es_write_reg(ES8388_DACCONTROL25, 0x1e); /* set LOUT2 / ROUT2 volume: 0dB (unattenuated) */ res |= es_write_reg(ES8388_DACCONTROL26, 0x10); res |= es_write_reg(ES8388_DACCONTROL27, 0x10); /* power up and enable DAC; power up ADC (no MIC bias) */ res |= es_write_reg(ES8388_DACPOWER, 0x3c); res |= es_write_reg(ES8388_DACCONTROL3, 0x00); if(res == ESP_OK) { ESP_LOGI(TAG, "ES8388 initializes OK"); } else { ESP_LOGI(TAG, "ES8388 initializes FAIL"); } return res; } esp_err_t setMicGain(es_mic_gain_t gain) { esp_err_t res = ESP_OK; uint8_t controlValue = (gain << 4) | gain; res |= es_write_reg(ES8388_ADCCONTROL1, controlValue); return res; } uint8_t getMicGain() { static uint8_t data; es_read_reg(ES8388_ADCCONTROL1, &data); data = data & 0x0f; return data; } esp_err_t setADCInput(es_adc_input_t input) { esp_err_t res = ESP_OK; uint8_t reg = 0; res = es_read_reg(ES8388_ADCCONTROL2, ®); reg = reg & 0x0f; res |= es_write_reg(ES8388_ADCCONTROL2, reg | input); if (input == ADC_INPUT_LINPUT2_RINPUT2) { res |= es_write_reg(ES8388_ADCCONTROL3, 0x80); } return res; } esp_err_t setADCVolume(uint8_t volume) { esp_err_t res = ESP_OK; if (volume > 100) volume = 100; uint16_t steps = (uint16_t)(((100 - volume) * 192) / 100); uint8_t data = (uint8_t)(steps); res |= es_write_reg(ES8388_ADCCONTROL8, data); res |= es_write_reg(ES8388_ADCCONTROL9, data); return res; } esp_err_t setDACVolume(uint8_t volume) { esp_err_t res = ESP_OK; volume = (volume > 100) ? 100 : volume; uint8_t steps = (uint8_t)(((uint16_t)(volume) * 33 + 50) / 100); steps = (steps > 0x21) ? 0x21 : steps; res |= es_write_reg(ES8388_DACCONTROL24, steps); res |= es_write_reg(ES8388_DACCONTROL25, steps); return res; } esp_err_t setDACOutput(es_dac_output_t output) { esp_err_t res = ESP_OK; res |= es_write_reg(ES8388_DACPOWER, output); return res; } // mute Output esp_err_t setDACmute(bool mute) { uint8_t _reg; es_read_reg(ES8388_ADCCONTROL1, &_reg); esp_err_t res = ESP_OK; if (mute) res |= es_write_reg(ES8388_DACCONTROL3, _reg | 0x02); else res |= es_write_reg(ES8388_DACCONTROL3, _reg & ~(0x02)); return res; } esp_err_t setMixSourceSelect(es_mixsel_t lmixsel, es_mixsel_t rmixsel) { esp_err_t res = ESP_OK; uint8_t left_bits = 0, right_bits = 0; switch (lmixsel) { case MIXLIN1: left_bits = 0b000; break; case MIXLIN2: left_bits = 0b001; break; case MIXADC: left_bits = 0b011; break; case MIXRES: return false; default: return false; } switch (rmixsel) { case MIXLIN1: right_bits = 0b000; break; case MIXLIN2: right_bits = 0b001; break; case MIXADC: right_bits = 0b011; break; case MIXRES: return false; default: return false; } uint8_t data = (left_bits << 3) | (right_bits << 0); res |= es_write_reg(ES8388_DACCONTROL16, data); return res; } esp_err_t setBitsSample(es_module_t mode, es_bits_length_t bits_len) { esp_err_t res = ESP_OK; uint8_t reg = 0; int bits = (int)bits_len; if (mode == ES_MODULE_ADC || mode == ES_MODULE_ADC_DAC) { res = es_read_reg(ES8388_ADCCONTROL4, ®); reg = reg & 0xe3; res |= es_write_reg(ES8388_ADCCONTROL4, reg | (bits << 2)); } if (mode == ES_MODULE_DAC || mode == ES_MODULE_ADC_DAC) { res = es_read_reg(ES8388_DACCONTROL1, ®); reg = reg & 0xc7; res |= es_write_reg(ES8388_DACCONTROL1, reg | (bits << 3)); } return res; } esp_err_t setSampleRate(es_sample_rate_t rate) { esp_err_t res = ESP_OK; uint8_t masterMode = 0x00; uint8_t adcFsRatio = 0x02; uint8_t dacFsRatio = 0x02; uint8_t mclkDiv = 0x00; switch (rate) { case SAMPLE_RATE_8K: // MCLK=12.288MHz adcFsRatio = 0x0A; // 01010 (MCLK/1536) dacFsRatio = 0x0A; break; case SAMPLE_RATE_11K: // MCLK=11.2896MHz adcFsRatio = 0x07; // 00111 (MCLK/1024) dacFsRatio = 0x07; break; case SAMPLE_RATE_16K: // MCLK=12.288MHz adcFsRatio = 0x06; // 00110 (MCLK/768) dacFsRatio = 0x06; break; case SAMPLE_RATE_24K: // MCLK=12.288MHz adcFsRatio = 0x04; // 00100 (MCLK/512) dacFsRatio = 0x04; break; case SAMPLE_RATE_32K: // MCLK=12.288MHz adcFsRatio = 0x03; // 00011 (MCLK/384) dacFsRatio = 0x03; break; case SAMPLE_RATE_44K: // MCLK=11.2896MHz adcFsRatio = 0x02; // 00010 (MCLK/256) dacFsRatio = 0x02; mclkDiv = 0x40; break; case SAMPLE_RATE_48K: adcFsRatio = 0x02; // 00010 (MCLK/256) dacFsRatio = 0x02; break; default: return false; } res |= es_write_reg(ES8388_MASTERMODE, masterMode | mclkDiv); res |= es_write_reg(ES8388_ADCCONTROL5, adcFsRatio & 0x1F); res |= es_write_reg(ES8388_DACCONTROL2, dacFsRatio & 0x1F); return res; }es8388.h:

/* * es8388.h * * Created on: Jul 31, 2021 * Author: xenir */ #ifndef ES8388_H_ #define ES8388_H_ #include "stdbool.h" #include "stdint.h" /** * @file ES8388_registers.h * @brief Definitions for ES8388 audio codec registers */ /** * @brief I2C device address for ES8388 */ #define ES8388_ADDR (0x10) /* ES8388 control registers */ /** * @brief Control register 1 - System control and clock settings */ #define ES8388_CONTROL1 (0x00) /** * @brief Control register 2 - Interface format and clock mode */ #define ES8388_CONTROL2 (0x01) /** * @brief Chip power management register */ #define ES8388_CHIPPOWER (0x02) /** * @brief ADC power control register */ #define ES8388_ADCPOWER (0x03) /** * @brief DAC power control register */ #define ES8388_DACPOWER (0x04) /** * @brief Low power control register 1 */ #define ES8388_CHIPLOPOW1 (0x05) /** * @brief Low power control register 2 */ #define ES8388_CHIPLOPOW2 (0x06) /** * @brief Analog volume management control */ #define ES8388_ANAVOLMANAG (0x07) /** * @brief Master/slave mode control */ #define ES8388_MASTERMODE (0x08) /* ADC registers */ /** * @brief ADC control 1 - Input selection and PGA gain */ #define ES8388_ADCCONTROL1 (0x09) /** @brief ADC control 2 - Digital mic settings */ #define ES8388_ADCCONTROL2 (0x0a) /** * @brief ADC control 3 - High-pass filter and ADC mode */ #define ES8388_ADCCONTROL3 (0x0b) /** * @brief ADC control 4 - Sample rate and clock divider */ #define ES8388_ADCCONTROL4 (0x0c) /** * @brief ADC control 5 - Digital volume control */ #define ES8388_ADCCONTROL5 (0x0d) /** * @brief ADC control 6 - ALC settings 1 */ #define ES8388_ADCCONTROL6 (0x0e) /** * @brief ADC control 7 - ALC settings 2 */ #define ES8388_ADCCONTROL7 (0x0f) /** * @brief ADC control 8 - ALC settings 3 */ #define ES8388_ADCCONTROL8 (0x10) /** * @brief ADC control 9 - Noise gate control */ #define ES8388_ADCCONTROL9 (0x11) /** * @brief ADC control 10 - Zero detection */ #define ES8388_ADCCONTROL10 (0x12) /** * @brief ADC control 11 - ALC enable and mode */ #define ES8388_ADCCONTROL11 (0x13) /** * @brief ADC control 12 - Left channel volume */ #define ES8388_ADCCONTROL12 (0x14) /** * @brief ADC control 13 - Right channel volume */ #define ES8388_ADCCONTROL13 (0x15) /** * @brief ADC control 14 - Analog PGA control */ #define ES8388_ADCCONTROL14 (0x16) /* DAC registers */ /** * @brief DAC control 1 - Soft ramp and volume control */ #define ES8388_DACCONTROL1 (0x17) /** * @brief DAC control 2 - DAC interface format */ #define ES8388_DACCONTROL2 (0x18) /** * @brief DAC control 3 - De-emphasis and mute control */ #define ES8388_DACCONTROL3 (0x19) /** * @brief DAC control 4 - Sample rate and clock divider */ #define ES8388_DACCONTROL4 (0x1a) /** * @brief DAC control 5 - Digital volume left */ #define ES8388_DACCONTROL5 (0x1b) /** * @brief DAC control 6 - Digital volume right */ #define ES8388_DACCONTROL6 (0x1c) /** * @brief DAC control 7 - Volume mixer control */ #define ES8388_DACCONTROL7 (0x1d) /** * @brief DAC control 8 - Mixer settings */ #define ES8388_DACCONTROL8 (0x1e) /** * @brief DAC control 9 - Channel swap and mute */ #define ES8388_DACCONTROL9 (0x1f) /** * @brief DAC control 10 - Zero cross detection */ #define ES8388_DACCONTROL10 (0x20) /** * @brief DAC control 11 - Volume ramp rate */ #define ES8388_DACCONTROL11 (0x21) /** * @brief DAC control 12 - Power management */ #define ES8388_DACCONTROL12 (0x22) /** * @brief DAC control 13 - Analog output control */ #define ES8388_DACCONTROL13 (0x23) /** * @brief DAC control 14 - Output phase control */ #define ES8388_DACCONTROL14 (0x24) /** * @brief DAC control 15 - Output level control */ #define ES8388_DACCONTROL15 (0x25) /** * @brief DAC control 16 - Mixer volume left */ #define ES8388_DACCONTROL16 (0x26) /** * @brief DAC control 17 - Mixer volume right */ #define ES8388_DACCONTROL17 (0x27) /** * @brief DAC control 18 - ALC control 1 */ #define ES8388_DACCONTROL18 (0x28) /** * @brief DAC control 19 - ALC control 2 */ #define ES8388_DACCONTROL19 (0x29) /** * @brief DAC control 20 - ALC control 3 */ #define ES8388_DACCONTROL20 (0x2a) /** * @brief DAC control 21 - ALC control 4 */ #define ES8388_DACCONTROL21 (0x2b) /** * @brief DAC control 22 - Noise gate control */ #define ES8388_DACCONTROL22 (0x2c) /** * @brief DAC control 23 - Zero detection */ #define ES8388_DACCONTROL23 (0x2d) /** * @brief DAC control 24 - Output mute control * */ #define ES8388_DACCONTROL24 (0x2e) /** * @brief DAC control 25 - Volume bypass control */ #define ES8388_DACCONTROL25 (0x2f) /** * @brief DAC control 26 - Output phase control */ #define ES8388_DACCONTROL26 (0x30) /** * @brief DAC control 27 - Volume fade control */ #define ES8388_DACCONTROL27 (0x31) /** * @brief DAC control 28 - Power on delay control */ #define ES8388_DACCONTROL28 (0x32) /** * @brief DAC control 29 - Output driver control */ #define ES8388_DACCONTROL29 (0x33) /** * @brief DAC control 30 - Reserved/test mode */ #define ES8388_DACCONTROL30 (0x34) /** * @brief Mixer input source selection * @note Mixer configuration affects audio path routing */ typedef enum { MIXLIN1, /**< Direct line input 1 (unprocessed signal path) */ MIXLIN2, /**< Direct line input 2 (alternative signal path) */ MIXRES, /**< Reserved mixer source (do not use in normal operation) */ MIXADC /**< Processed signal from ADC/ALC (with automatic level control) */ } es_mixsel_t; /** * @brief ES8388 functional module selection */ typedef enum { ES_MODULE_MIN = -1, /**< Minimum module selector (validation flag) */ ES_MODULE_ADC = 0x01, /**< Enable ADC module */ ES_MODULE_DAC = 0x02, /**< Enable DAC module */ ES_MODULE_ADC_DAC = 0x03, /**< Enable both ADC and DAC modules */ ES_MODULE_LINE = 0x04, /**< Line-in/out interface control */ ES_MODULE_MAX /**< Maximum module selector (validation flag) */ } es_module_t; /** * @brief Audio data bit length configuration * @note Actual supported resolution depends on hardware capabilities */ typedef enum { BIT_LENGTH_MIN = -1, /**< Minimum bit length flag (validation) */ BIT_LENGTH_16BITS = 0x03, /**< 16-bit word length */ BIT_LENGTH_18BITS = 0x02, /**< 18-bit word length */ BIT_LENGTH_20BITS = 0x01, /**< 20-bit word length */ BIT_LENGTH_24BITS = 0x00, /**< 24-bit word length (typical default) */ BIT_LENGTH_32BITS = 0x04, /**< 32-bit word length */ BIT_LENGTH_MAX, /**< Maximum bit length flag (validation) */ } es_bits_length_t; /** * @brief ADC input channel selection * @note Configuration affects both left and right channels */ typedef enum { ADC_INPUT_LINPUT1_RINPUT1 = 0x00, /**< Use input 1 for both channels */ ADC_INPUT_LINPUT2_RINPUT2 = 0x10, /**< Use input 2 for both channels */ ADC_INPUT_DIFFERENCE1 = 0xf0, /**< Differential input configuration */ } es_adc_input_t; /** * @brief DAC output channel selection * @note Multiple outputs can be combined using bitwise OR */ typedef enum { DAC_OUTPUT_OUT1 = 0x30, /**< Enable output channel 1 */ DAC_OUTPUT_OUT2 = 0x0C, /**< Enable output channel 2 */ DAC_OUTPUT_ALL = 0x3c, /**< Enable all output channels */ } es_dac_output_t; /** * @brief Microphone gain settings * @note Values represent gain steps in 3dB increments */ typedef enum { MIC_GAIN_0DB = 0, /**< 0dB microphone gain */ MIC_GAIN_3DB, /**< 3dB microphone gain */ MIC_GAIN_6DB, /**< 6dB microphone gain */ MIC_GAIN_9DB, /**< 9dB microphone gain */ MIC_GAIN_12DB, /**< 12dB microphone gain */ MIC_GAIN_15DB, /**< 15dB microphone gain */ MIC_GAIN_18DB, /**< 18dB microphone gain */ MIC_GAIN_21DB, /**< 21dB microphone gain */ MIC_GAIN_24DB, /**< 24dB microphone gain (maximum) */ } es_mic_gain_t; typedef enum { SAMPLE_RATE_8K = 0, /**< 8000 Hz sampling rate */ SAMPLE_RATE_11K, /**< 11025 Hz sampling rate */ SAMPLE_RATE_16K, /**< 16000 Hz sampling rate */ SAMPLE_RATE_24K, /**< 24000 Hz sampling rate */ SAMPLE_RATE_32K, /**< 32000 Hz sampling rate */ SAMPLE_RATE_44K, /**< 44100 Hz sampling rate (CD quality) */ SAMPLE_RATE_48K /**< 48000 Hz sampling rate (professional audio) */ } es_sample_rate_t; // API esp_err_t es_write_reg(uint8_t reg, uint8_t data); esp_err_t es_read_reg(uint8_t reg, uint8_t *data); esp_err_t es8388_init(void); esp_err_t es8388_init2(void); esp_err_t setMicGain(es_mic_gain_t gain); uint8_t getMicGain(); esp_err_t setADCInput(es_adc_input_t input); esp_err_t setADCVolume(uint8_t volume); esp_err_t setDACVolume(uint8_t volume); esp_err_t setDACOutput(es_dac_output_t output); esp_err_t setDACmute(bool mute); esp_err_t setMixSourceSelect(es_mixsel_t lmixsel, es_mixsel_t rmixsel); esp_err_t setBitsSample(es_module_t mode, es_bits_length_t bits_len); esp_err_t setSampleRate(es_sample_rate_t rate); void es8388_dump_registers(void); esp_err_t es8388_check_connection(void); #endif /* ES8388_H_ */driver works but I still have a problem with left ADC, I do measures with generator -> audioModule -> M5Stack Code S3 SE -> DSP bypass in code -> audioModule -> interface audio on my PC. I check 440 Hz on rigth and left channel, white noise, and also I check only DAC outputs and DAC seems to work properly. Maybe my audioModule is broken? Something

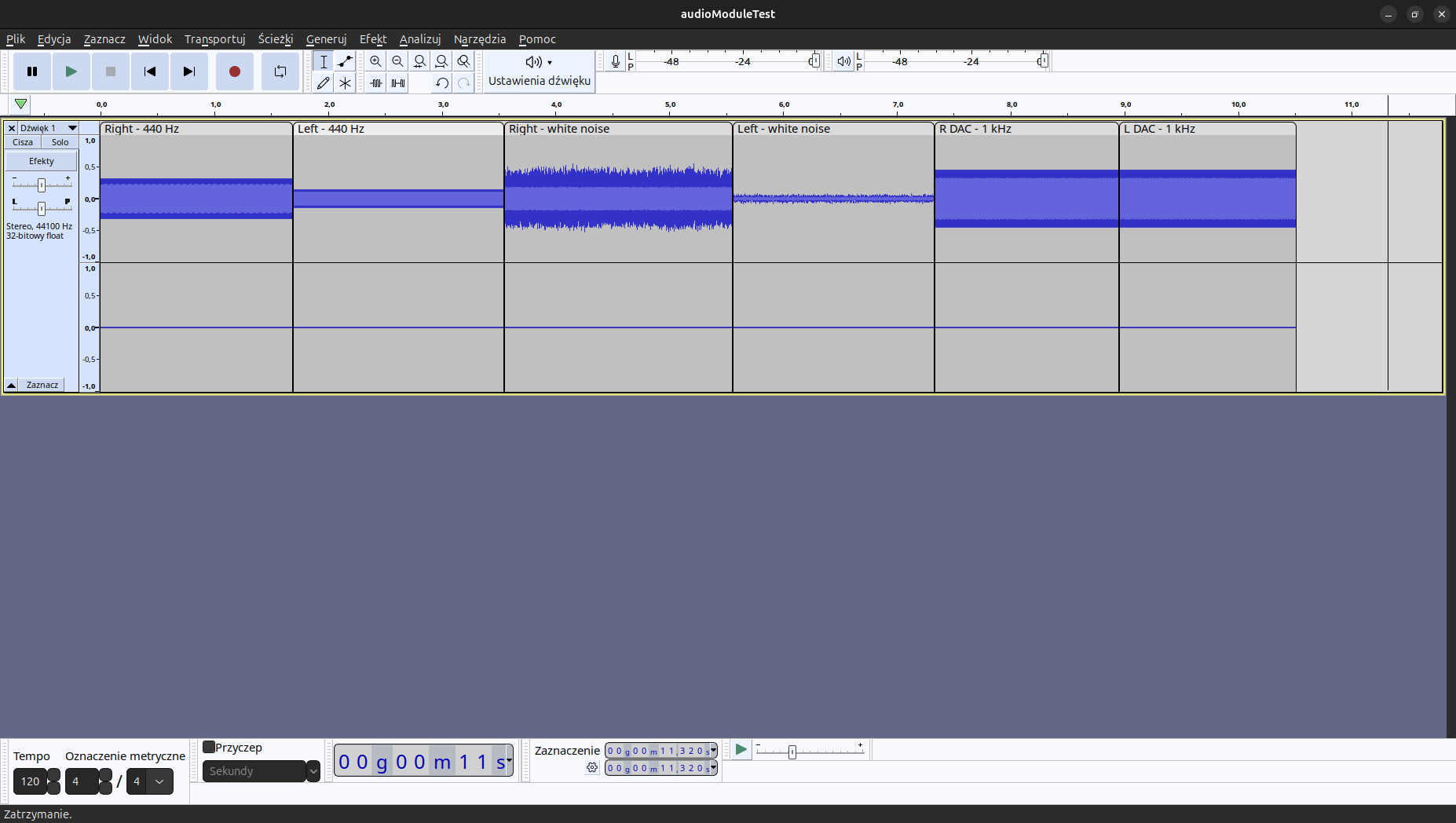

wrong with left ADC circuit or es83388 chip.waveforms

R bypass 440 Hz

L bypass 440 Hz

R bypass white noise

L bypass white noise

R DAC 1kHz

L DAC 1 kHz

You can see that signal on left ADC channel have lower amplitude and frequency analysis with white noise shows that left ADC is not "flat" like on right channel.

DAC outputs have the same amplitude so DAC works good. -

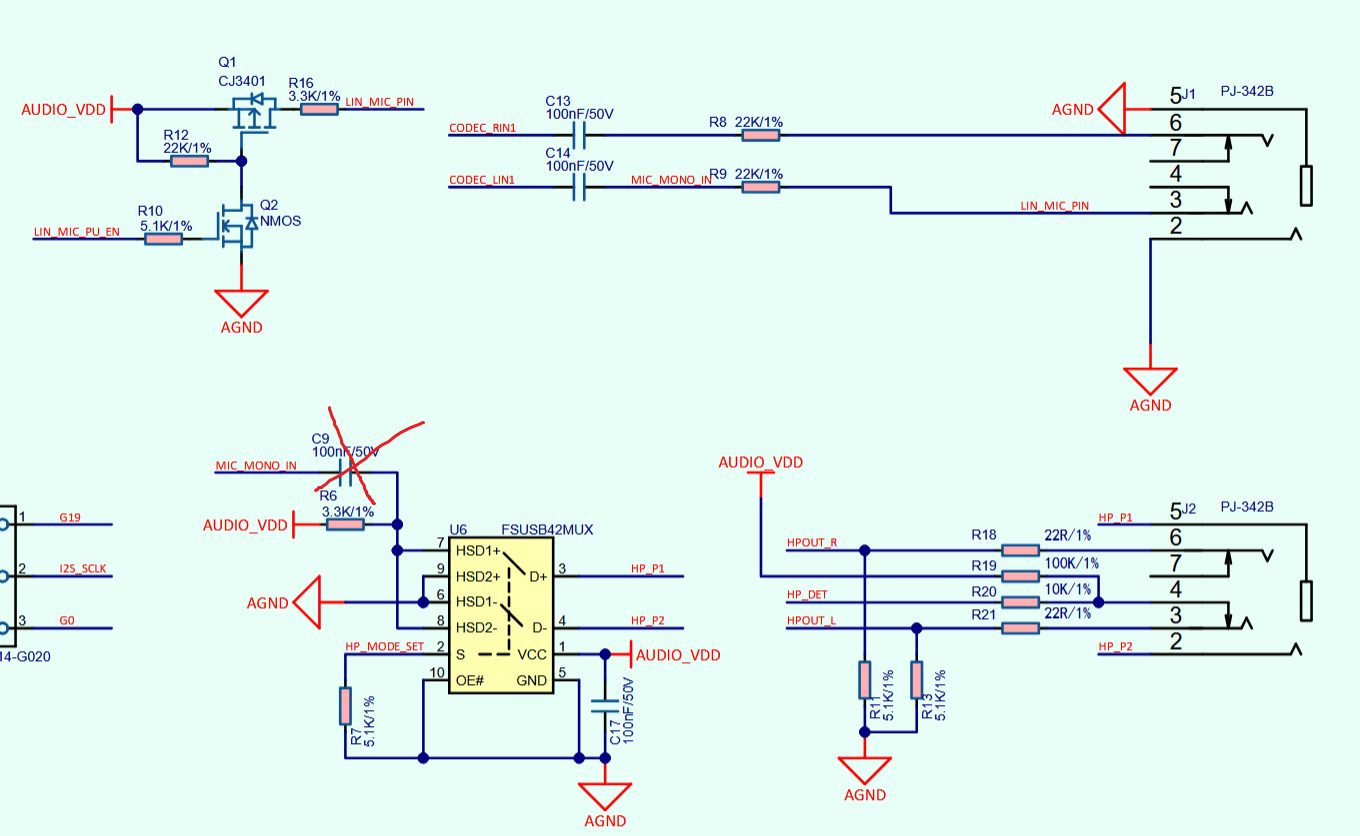

I fix the problem by remove condensator C9

Hello! It looks like you're interested in this conversation, but you don't have an account yet.

Getting fed up of having to scroll through the same posts each visit? When you register for an account, you'll always come back to exactly where you were before, and choose to be notified of new replies (either via email, or push notification). You'll also be able to save bookmarks and upvote posts to show your appreciation to other community members.

With your input, this post could be even better 💗

Register Login