Port.C of boot serial console is IO inverted on CoreMP135.

-

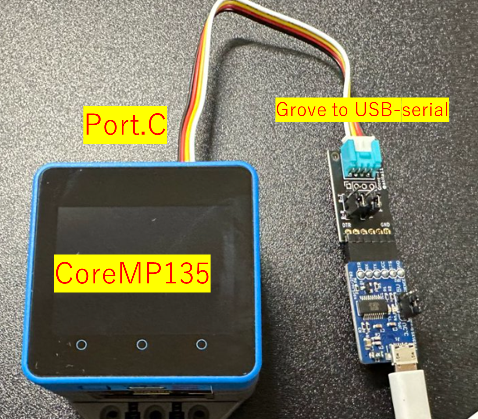

The boot serial console can be accessed from Grove Port.C on the CoreMP135, via USB serial.

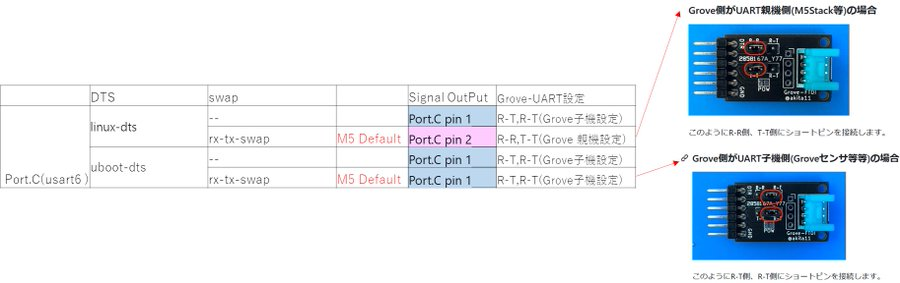

U-Boot logs are output from Port.C pin 1 (non TX-RX swap signal), while the Linux console is output from Port.C pin 2 (with TX-RX swap signal).

I would like to see the U-Boot logs and Linux console aligned on the same IO.

- U-Boot logs

from Port.C non TX-RX swap signal

NOTICE: CPU: STM32MP135D Rev.Y NOTICE: Model: STMicroelectronics STM32MP135F-DK Discovery Board NOTICE: BL2: v2.6-stm32mp1-r1.0(release):2021.05-10169-gb885d5525a NOTICE: BL2: Built : 15:39:25, May 15 2024 NOTICE: BL2: Booting BL32 optee optee: OP-TEE: revision 3.16 (b885d552) U-Boot 2021.10-stm32mp-r1 (May 15 2024 - 15:39:22 +0800) CPU: STM32MP135D Rev.? Model: STMicroelectronics STM32MP135F-DK Discovery Board Board: stm32mp1 in trusted mode (st,stm32mp135f-dk) DRAM: 512 MiB optee optee: OP-TEE: revision 3.16 (b885d552) Clocks: - MPU : 650 MHz - AXI : 266.500 MHz - PER : 24 MHz - DDR : 533 MHz WDT: Started with servicing (32s timeout) NAND: 0 MiB MMC: STM32 SD/MMC: 0 Loading Environment from MMC... OK In: serial Out: serial Err: serial invalid MAC address 0 in OTP 00:00:00:00:00:00 Net: No ethernet found. Hit any key to stop autoboot: 0 Boot over mmc0! switch to partitions #0, OK mmc0 is current device Scanning mmc 0:5... Found /boot/extlinux/extlinux.conf Retrieving file: /boot/extlinux/extlinux.conf 160 bytes read in 20 ms (7.8 KiB/s) 1: stm32mp135f-coremp135-buildroot Retrieving file: /boot/zImage 7923832 bytes read in 579 ms (13.1 MiB/s) append: root=/dev/mmcblk0p5 rw panic=5 quiet rootwait Retrieving file: /boot/stm32mp135f-coremp135.dtb 68116 bytes read in 24 ms (2.7 MiB/s) Kernel image @ 0xc2000000 [ 0x000000 - 0x78e878 ] ## Flattened Device Tree blob at c4000000 Booting using the fdt blob at 0xc4000000 Loading Device Tree to cffec000, end cffffa13 ... OK gc2145@3c node not found - DT update aborted FDT: cryp@54002000 node disabled for STM32MP135D Rev.? Starting kernel ...- Linux logs

from Port.C with TX-RX swap signal

[ 0.004005] /cpus/cpu@0 missing clock-frequency property [ 0.435138] stm32-cpufreq stm32-cpufreq: OPP-v2 not supported Starting syslogd: OK Starting klogd: OK Starting modules: soundcore success, snd success, snd_timer success, snd_pcm success, snd_pcm_dmaengine success, snd_soc_core success, snd_soc_simple_card_utils success, snd_soc_audio_graph_card success, snd-soc-simple-card success, snd_soc_stm32_sai success, snd_soc_stm32_sai_sub success, cdc-acm success, libcomposite success, g_serial success, OK Running sysctl: OK Starting mdev... OK Seeding 256 bits and crediting Saving 256 bits of creditable seed for next boot Starting tee-supplicant: Using device /dev/teepriv0. OK Starting network: OK Starting dhcpcd... dhcpcd-9.4.1 starting DUID 00:01:00:01:2d:f9:ec:09:2a:88:82:9b:b0:f0 forked to background, child pid 177 [ 5.966541] m_can_platform 4400e000.can can0: bit-timing not yet defined [ 5.974064] m_can_platform 4400e000.can can0: failed to open can device [ 5.988759] m_can_platform 4400f000.can can1: bit-timing not yet defined [ 5.994164] m_can_platform 4400f000.can can1: failed to open can device Starting dropbear sshd: OK Stopping /etc/rc.localOK # # ####### ##### ####### # ##### # # ## ## # # # # # # # # # # # # # # # # # # # # # # # # # ###### ##### # # # # ### # # # # # ####### # # # # # # # # # # # # # # # # # # ##### ##### # # # ##### # # Welcome to CoreMP135, Powered by M5Stack. CoreMP135 login:Reference

- U-Boot logs

-

The uart6 in linux-dts was able to switch IO with rx-tx-swap.

The uart6 in uboot-dts seems to be fixed, unable to switch IO with rx-tx-swap.

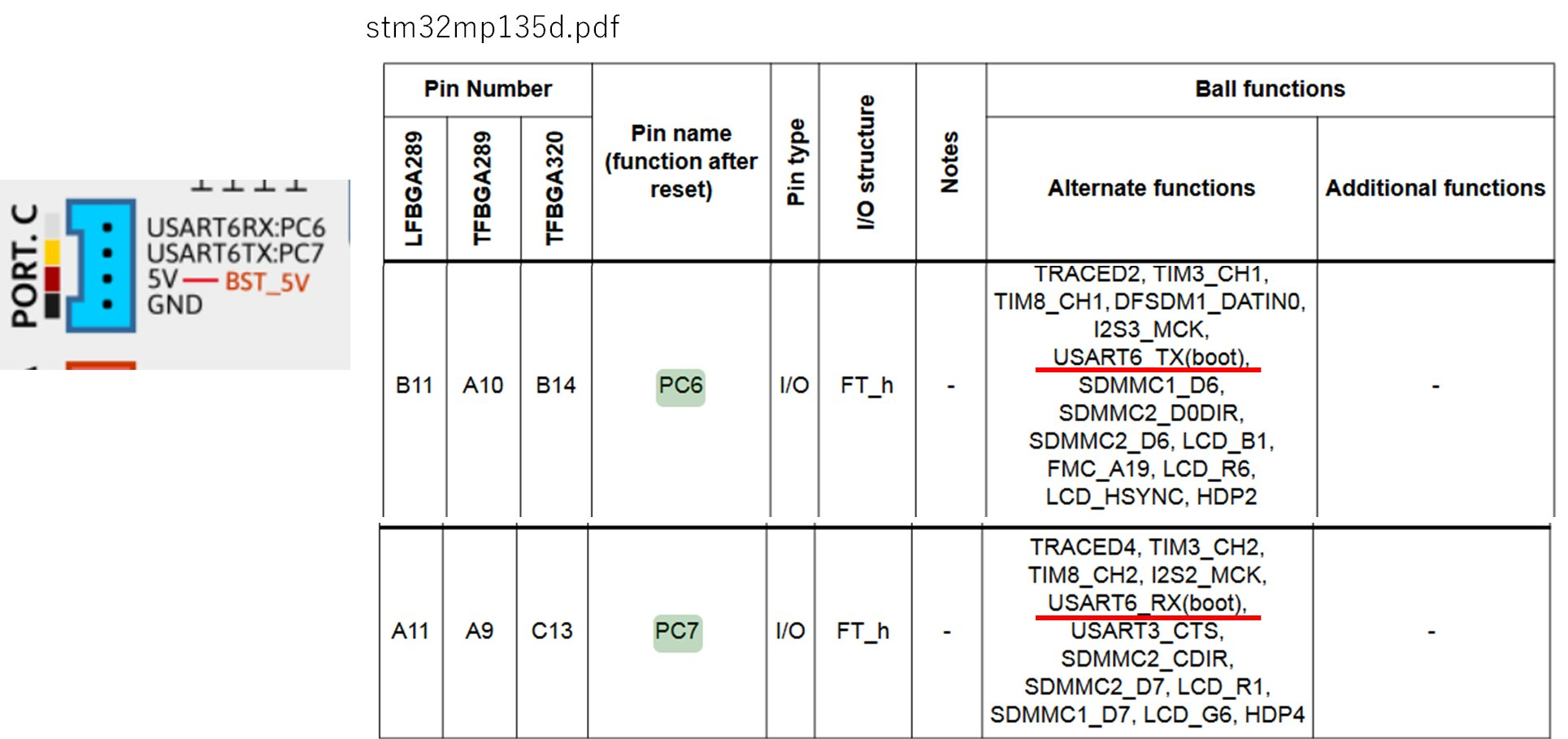

Is there a HW issue with the Stm32MP135?

-

According to the data sheet, is the IO of UART6 fixed at startup?

Reference:

https://www.st.com/ja/microcontrollers-microprocessors/stm32mp135d.html -

@nnn Yes its set at startup by the device tree overlay file.

I finally managed to find the config in the linux DTS file last night.

In order to redefine it you need to create a new Device Tree config to redefine the pins and functions. -

This discussion will be continued below

https://github.com/m5stack/CoreMP135_buildroot-external-st/issues/2

Hello! It looks like you're interested in this conversation, but you don't have an account yet.

Getting fed up of having to scroll through the same posts each visit? When you register for an account, you'll always come back to exactly where you were before, and choose to be notified of new replies (either via email, or push notification). You'll also be able to save bookmarks and upvote posts to show your appreciation to other community members.

With your input, this post could be even better 💗

Register Login